# Óbuda University

PhD Thesis

## High Performance Image Sensor Processing using Field Programmable Gate Arrays

Gábor Szedő Becker

Supervisor:

Róbert Lovas, PhD, habil.

## Doctoral School of Applied Informatics and Applied Mathematics

Budapest, 2023.

### **Final Examination Committee**

Chair: Prof. Dr. József Tar, PhD, habil, DSc

### Members: Dr. Zoltán Vámossy, PhD Dr. Antal Hiba, PhD (SZTAKI)

**Date of Final Examination:** April 11, 2022

### Full Committee of Public Defense

Opponents: Dr. Zoltán Vámossy, PhD Dr. Zoltán Nagy, PhD (PPKE)

Chair: Prof. Dr. József Tar, PhD, habil, DSc

> Secretary: Dr. Eszter Kail, PhD

#### Members:

Prof. Dr. Sándor Szénási, PhD, habil Dr. Ákos Odry, PhD Dr. Antal Hiba, PhD (SZTAKI)

> Date of Public Defense: March 6, 2023

## Declaration

I, the undersigned, **Gabor Szedo Becker**, hereby state and declare that this Ph.D. thesis represents my own work and is the result of my own original research. I only used the sources listed in the references. All parts taken from other works, either as word for word citation or rewritten keeping the original meaning, have been unambiguously marked, and reference to the source was included.

Bern he Son

Gabor Szedo Becker

## Nyilatkozat

Alulírott **Becker Szedő Gábor** kijelentem, hogy ez a doktori értekezés a saját munkámat mutatja be, és a saját eredeti kutatásom eredménye. Csak a hivatkozásokban fel- sorolt forrásokat használtam fel, minden más munkából származó rész, a szó szerinti, vagy az eredeti jelentést megtartó átiratok egyértelműen jelölve, és forrás hivatkozva lettek.

Bern lit (

Becker Szedő Gábor

## Contents

| High I      | Performance Image Sensor Processing using Field Programmable Gate Arrays | i    |

|-------------|--------------------------------------------------------------------------|------|

| Declar      | ation                                                                    | iii  |

| Nyilat      | kozat                                                                    | iv   |

| Conte       | nts                                                                      | v    |

| Ackno       | wledgements                                                              | vii  |

| Köszö       | netnyilvánítás                                                           | viii |

| Abstra      | nct                                                                      | ix   |

|             | at                                                                       |      |

| 05          | teljesítményű szenzor képfeldolgozás FPGA áramkörökkel                   |      |

|             | eviations & notations                                                    |      |

|             | Figures                                                                  |      |

| List of     | Tables                                                                   |      |

| 1           | Introduction                                                             | 1    |

| 1.1         | Field Programmable Gate Arrays                                           |      |

| 1.2         | Signal and Video Processing                                              |      |

| 2           | Image Signal Processing                                                  |      |

| 2.1         | Flat-Field Correction                                                    |      |

| 2.2         | Defective Pixel Correction                                               |      |

| 2.3         | Color Filter Array Interpolation                                         |      |

| 2.4         | Image Statistics                                                         |      |

| 2.5         | Color Correction Matrix                                                  |      |

| 2.6         | Tone Curve Correction                                                    |      |

| 2.7         | Color-Space Conversion                                                   |      |

| 2.8         | Noise Reduction                                                          |      |

| 2.9         | Edge Enhancement                                                         |      |

| 2.10        | Lens Shading Correction                                                  |      |

| 2.11        | Image de-warping                                                         |      |

| 2.12        | Video Scaling                                                            |      |

| 2.13        | Chroma resampling                                                        |      |

| 2.14        | ISP Sensor Control                                                       |      |

| 2.15        | Chapter Summary                                                          |      |

| 3           | Image Sensor Uniformity Correction                                       |      |

| 3.2         | A Linear model of Spatial Non-Uniformity                                 |      |

| 3.3         | Motivation                                                               |      |

| 3.4         | Uniformity Calibration Method                                            |      |

| 3.5         | Hardware Implementation of Flat-Field Correction                         |      |

| 3.6         | Related Work                                                             |      |

| 3.7         | DSNU Analysis                                                            |      |

| 3.8         | PRNU Analysis                                                            |      |

| 3.9<br>3.10 | Lens Shading                                                             |      |

| 3.10<br>4   | Chapter Summary<br>Defective Pixel Correction                            |      |

|             |                                                                          |      |

| 4.1         | Pixel Defect Types                                                       |      |

| 4.2  | Static Identification                                          |    |

|------|----------------------------------------------------------------|----|

| 4.3  | Dynamic Identification                                         |    |

| 4.4  | Related Work                                                   |    |

| 4.5  | Proposed Solution                                              |    |

| 4.6  | Constrained Randomization                                      | 49 |

| 4.7  | Flicker defects                                                |    |

| 4.8  | Hardware Implementation                                        |    |

| 4.9  | DP candidate list implementation                               | 51 |

| 4.10 | Interpolation                                                  |    |

| 4.11 | Parameterization                                               | 53 |

| 4.12 | Results                                                        | 54 |

| 4.13 | Chapter Summary                                                | 54 |

| 5    | White Balance Correction                                       | 55 |

| 5.1  | White Balance                                                  | 56 |

| 5.2  | Related Work                                                   |    |

| 5.3  | Dynamic illuminant colorimetry                                 | 59 |

| 5.4  | Heuristics for color constancy                                 | 60 |

| 5.5  | Proposed Algorithm                                             | 61 |

| 5.6  | Results                                                        | 70 |

| 5.7  | Chapter Summary                                                | 71 |

| 6    | Non-linear filter optimizations                                |    |

| 6.1  | Median and Rank order Filtering                                | 72 |

| 6.2  | 2D Rank Order Filtering                                        | 75 |

| 6.3  | Virtual and non-rectangular kernels                            |    |

| 6.4  | Results                                                        | 79 |

| 6.5  | Chapter Summary                                                | 80 |

| 7    | Efficient Implementations of Fast Fourier Transform processors | 81 |

| 7.1  | Design considerations                                          | 81 |

| 7.2  | Memory Segmentation                                            | 82 |

| 7.3  | Natural to Digit-reversed reordering                           |    |

| 7.4  | Implementation Results                                         |    |

| 7.5  | Chapter summary                                                |    |

| 8    | Direct Digital Synthesis                                       |    |

| 8.1  | Introduction                                                   |    |

| 8.2  | Current Solutions                                              | 92 |

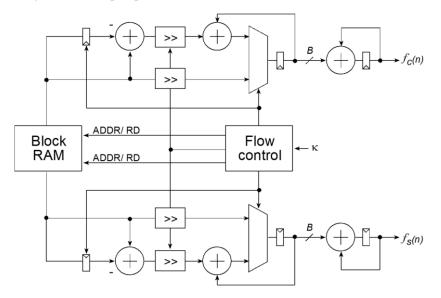

| 8.3  | Digital Resonators                                             |    |

| 8.4  | Quadratic interpolation                                        | 93 |

| 8.5  | Cascaded Resonator Interpolator structure                      |    |

| 8.6  | Chapter Summary                                                |    |

|      | ndix                                                           |    |

| 9    | Bibliography                                                   |    |

| 9.1  | Publications related to the dissertation                       |    |

| 9.2  | Other, non-related publications                                |    |

## Acknowledgements

I would like to thank my doctoral supervisor *Róbert Lovas, PhD habil.* for his valuable support during my doctoral studies at the Óbuda University. His relentless encouragement, rigorous reviews and high scientific standards was a key factor to the successful completion of this work. I highly appreciate the support of *Gábor Kertész, PhD,* and *Ákos Hajnal, PhD,* who were supporting my research with guidance about the PhD program with practical advice, inspired me with their unyielding commitment to science, neural networks and AI.

I would also like to thank *Ted Babpty, PhD* for the opportunity and support during my research scholarship at Vanderbilt University. Ted supported my work in the research of FGPA implementation of FFTs both professionally and by securing research grants, which culminated in our paper accepted for an international conference on FPGAs.

I would like to express my gratitude to my late advisor, *Béla Fehér, PhD*, who introduced me to the world of programmable logic as an MSc student, and later allowed me to join the Department of Measurement and Instrumentation Systems at the Budapest University of Technology and Economics, as a graduate student. Béla introduced me to academia, provided guidance writing my first papers, and provided a professional background, inspiring environment, and opportunities to attend my first international conferences. Also at the department of Measurement and Information Systems, I would like to recognize the efforts of *Péter Szántó*. With Péter we ran labs, delivered courses, collaborated on projects, developed novel filter architectures, wrote papers and patents. Péter has been a stable source of professional advice, a great co-author and friend.

My commendation and gratitude are also due to Professor *Christopher Dick, PhD*, who offered me a position at Xilinx Inc, which provided access to cutting edge technology and collaboration with some of the best minds of Silicon Valley. While most for-profit corporations encourage capturing inventions and new scientific content in patents, Chris also found ways to publish our work at scientific conferences.

Special thanks to *Wilson Chung, PhD,* who encouraged me to lead the image sensor interface IP team at Xilinx, which was my first foray into the world of Image Signal Processing (ISP). Wilson is a pragmatic leader and talented architect with an excellent overview of contemporary silicon capabilities and detailed understanding of image and video processing algorithms.

Last, but not least, I owe special thanks to my family who put up with many weekends spent at home while I was working on the dissertation.

## Köszönetnyilvánítás

Szeretnék köszönetet mondani doktori témavezetőmnek, *Dr. habil. Lovas Róbert*nek, az Óbudai Egyetemen végzett doktori tanulmányaim során nyújtott értékes segítségért. Róbert tudományos közreműködése, észrevételei, tanácsai, magas szintű szakmai vezetése nélkül ez a disszertáció nem készült volna el.

Nagyon nagyra becsülöm *Dr. Kertész Gábor* és *Dr. Hajnal Ákos* segítségét, a PhD programmal kapcsolatos gyakorlati tanácsaikat, közös kutatási, szakmai, és publikációs tevékenységüket, valamint lankadatlan elkötelezettségüket a számítástechnika, a neurális hálózatok, és a mesterséges intelligencia témakörében.

Meg szeretném köszönni *Dr. Ted Bapty* professzornak a lehetőséget, hogy kutatói munkatársként részt vehetettem a Vanderbilt Egyetem Szoftver Integrált Rendszerek tanszékének munkájában. Ez az egy év meghatározó volt az életemben. Ted pályázatainak és szakmai támogatásának köszönhetem kutatói munkám FFT struktúrák FPGA megvalósításával foglalkozó ágát, és az első közös cikkünket, amelyet befogadtak publikációra egy FPGA témájú tudományos konferenciára az Egyesült Államokban.

Hálával tartozom a tragikus körülmények között elhunyt *Dr. Fehér Béla* professzornak, aki még MSc hallgatóként bevezetett a programozható logikai áramkörök világába, és megadta a lehetőséget, hogy képviselhessem a Budapesti Műszaki Egyetemet Magyarország első FPGA programozási versenyén. Első helyezésünkért felvételt nyertem a Méréstechnika és Információs Rendszerek tanszék PhD programjára, és ezzel az akadémiai munkába. Béla vezetése alatt írtam meg első cikkeimet, neki köszönhetem az első konferencia előadásaimat, és az első nemzetközi konferencia publikációkat.

Szerzőtársaim közül szeretném kiemelni, és köszönetet mondani *Szántó Péternek*, akivel PhD hallgatóként együtt kutattunk, oktattunk, és vezettünk hallgatói laborokat. Péterrel sok közös projektünk, publikációnk és egy amerikai szabadalmunk is született.

Hasonlóan köszönöm és nagyra értékelem *Dr. Christopher Dick* professzor segítségét, aki a Melbourne-i Egyetemtől csatlakozott a Xilinx cég IP fejlesztő csoportjához, és tudományos munkám alapján pozíciót ajánlott a jelfeldolgozási csoportban. Chris-en keresztül bevezetést nyertem a legújabb FPGA technológiákba, és a Szilícium Völgy számos szakemberével ismerkedhettem meg közös kutatás-fejlesztési munkánk során.

Köszönettel tartozom *Dr. Wilson Chung*-nak, hogy bevont a Xilinx kép-, és video feldolgozó csoport alapításába, és rám bízta a szenzor interfész csoport vezetését. Ezzel nyertem bevezetést a CCD és CMOS szenzorok, valamint az ISP-k világába.

Végül, de nem utolsó sorban hálával tartozom családomnak, hogy kitartottak mellettem az évek során amíg ez a disszertáció megszülethetett.

## Abstract

## High Performance Image Sensor Processing using Field Programmable Gate Arrays

Image sensors are ubiquitous parts of everyday life, present in mobile phones, laptops, tablets, cars, Internet of Things (IoT) and security devices. Most camera products are prototyped using programmable logic. Low volume special cameras, such as Infrared (IR) imaging Focal Plane Arrays (FPAs) and high frame-rate industrial, scientific cameras use Field Programmable Gate Arrays (FPGAs) in the released version of the product as well.

Meanwhile FPGAs transformed from a uniform sea-of-gates architecture to a heterogenous multiprocessing System-on-a-Chip (SoC) platform, capable of implementing not only glue-logic but complex signal-, and image processing algorithms.

In Chapter 1, this dissertation first reviews recent progress in FPGA architecture and technology. Similarly, Chapter 2 introduces the function and architecture of Image Signal Processor (ISP) modules. The following chapters detail my contributions to new algorithms, architectures or methods on the field of ISP implementation on FPGAs, organized by topic matching thesis points.

Chapter 3 is devoted to uniformity correction of CMOS image sensors. I present my analysis of fixed-pattern noise and compare multiple practical approaches to reduce noise.

Chapter 4 describes a method to dynamically detect and interpolate pixel defects without access to a frame buffer.

Chapter 5 concentrates on image quality improvements, with focus on noise reduction. Median filters, a subclass of rank order filters, are widely used for noise reduction while preserving edges is signals and images. Optimizations of 1D/2D rank order filter structures for FPGA implementation are explored.

Chapter 6 describes my work on Automatic White Balance adjustment. Low-latency algorithms are provided for simple, robust control of sensor parameters based on image statistics collected on the fly.

Chapter 7 focuses on frequency domain filtering and efficient implementation of widely used image-, and signal processing functions: one, and Two-dimensional Fast Fourier Transforms. I propose optimizations in the storage and access sequencing of intermediate results, which reduces local BRAM allocation by 50%.

In Chapter 8 I propose a resonator based Direct Digital Synthesis (DDS) module, which allows further reduction in memory allocation.

## Kivonat

### Nagy teljesítményű szenzor képfeldolgozás FPGA áramkörökkel

A képfelvevő szenzorok mára szinte mindenütt jelen vannak. Mobiltelefonokban, laptopokban, gépjárművekben, biztonsági és IoT rendszerekben egyre több szenzor szolgáltat képeket, videókat. Ezen rendszerek többségét programozható logikai áramkörökkel fejlesztik. A kis-szériás, nagyfelbontású, ultra gyors kamerák, és speciális (pl. infravörös) kamerák kereskedelmi forgalomba került változatai is a Field Programmable Gate Array (FPGA) áramkörökre épülnek. Az elmúlt évtizedekben az FPGA áramkörök kezdeti homogén, sea-of-gates architektúráját kiegészítették lokális memóriákkal, jelfeldolgozó, és általános célú processzorokkal, számítástechnikai rendszereket (SoC) valósítva meg egyetlen chipen.

A disszertáció első fejezetében bemutatom az FPGA áramkörök alkotóelemeit, és a digitális jel-, és kép-feldolgozás szempontjából kritikus alapmodulok implementációját. A második fejezet a kamera előfeldolgozó (ISP) áramkörök moduljainak funkcióit, és ezek FPGA-n belüli megvalósítását mutatja be. A harmadik fejezet a CMOS szenzorok fixmintázatú zaját, ennek hőmérséklet és paraméter függőségét elemzi, illetve vizsgálja a különböző kompenzációs stratégiák komplexitását és teljesítményét. A negyedik fejezetben kitérek a pixel hibák osztályozására, és megoldást mutatok a hibák dinamikus feltérképezésére és interpolációjára külső memória hozzáférés nélkül.

Az ötödik fejezet a zajelnyomást, ezen belül a nem-lineáris szűrők FPGA alapú optimális megvalósítását taglalja. A medián-, és rank-szűrők eredményesen használhatók kiugró minták szűrésére, élességromlás nélkül. A gyakorlatban jól alkalmazható, és FPGA megvalósításra optimalizált algoritmust adok egy-, és kétdimenziós rank szűrők megvalósítására.

A hatodik fejezet a fehéregyensúly valós idejű automatikus beállítására mutat algoritmust. Az ISP áramkör statisztikai moduljának jeleit egy kompakt, FPGA áramkörökön belül megvalósítható neurális hálózattal értékelve, gyors és a jelenlegi beágyazott megoldásoknál pontosabb megoldást mutatok be.

A hetedik fejezet a frekvencia tartományban végzett jel-, és képfeldolgozó algoritmusok alapját képező diszkrét gyors Fourier Transzformáció (FFT) FPGA optimalizációját vizsgálja. A javasolt megoldásokkal a transzformáció elvégzéséhez szükséges lokális memória felére csökkenthető, illetve a szükséges konstans faktorok valós idejű számításával a megvalósításhoz szükséges szilícium terület jelentősen csökkenthető.

A nyolcadik fejezet az FFT számításhoz szükséges komplex egységvektorok számítására mutat optimális megoldásokat FPGA áramkörökön belül.

## Abbreviations & notations

In this study the following notations and abbreviations were used:

| AE Automatic Exposure adjustment                          |              |

|-----------------------------------------------------------|--------------|

| ASIC Application Specific Integrated Circuit              |              |

| ASSP Application Specific Standard Parts                  |              |

| AWB Automatic White Balance adjustment                    |              |

| BRAM 18-, or 36 kbit dual ported Block RAM primitive in F | FPGA devices |

| CCM Color Correction Matrix                               |              |

| CFA Color Filter Array                                    |              |

| CMOS Complementary Metal Oxide Semiconductor              |              |

| CNN Convolutional Neural Network                          |              |

| DCT Discrete Cosine Transform                             |              |

| DDS Direct Digital Synthesis                              |              |

| DIF Decimation In Frequency                               |              |

| DIT Decimation In Time                                    |              |

| DPC Defective Pixel Correction                            |              |

| DSNU Dark Signal Non-Uniformity                           |              |

| DSP Digital Signal Processing                             |              |

| FFC Flat-Field Correction                                 |              |

| FFT Fast Fourier Transform                                |              |

| FPGA Field Programmable Gate Array                        |              |

| FPR Fixed-Point Representation                            |              |

| GPU Graphical Processing Unit                             |              |

| HDL Hardware Description Language                         |              |

| ISP Image Signal Processor                                |              |

| IoT Internet of Things                                    |              |

| LUT Look Up Table                                         |              |

| MANR Motion Adaptive Noise Reduction                      |              |

| MIMO Multiple Input, Multiple Output                      |              |

| PCC Pearson Correlation Coefficient                       |              |

| PRNU Photon Response Non-Uniformity                       |              |

| QDDFS Quadrature Direct Digital Frequency Synthesizer     |              |

| SFDR Spurious Free Dynamic Range                          |              |

| SISD Single Instruction Single Data                       |              |

| SIMD Single Instruction Multiple Data                     |              |

| SoC System on a Chip                                      |              |

| SNR Signal to Noise Ratio                                 |              |

# **List of Figures**

| Figure 1: Simple Sea of Gates FPGA architecture                                                 | 1  |

|-------------------------------------------------------------------------------------------------|----|

| Figure 2: Example block diagram of a modern FPGA device                                         | 2  |

| Figure 3: Example implementation of a machine vision platform                                   | 5  |

| Figure 4: Streaming ISP pipeline HW and FW components                                           | 6  |

| Figure 5. Examples of the Bayer RGB Color Filter Array pattern (left: RGB, right CMY)           | 7  |

| Figure 6. Examples of CFA interpolation color artifacts (left: Zoneplate, right: Lighthouse)    |    |

| Figure 7: 12 bit gamma correction module with interpolation                                     | 9  |

| Figure 8: Conceptual conversion between the RGB and YCrCb color-spaces                          | 10 |

| Figure 9: Flat-field image demonstrating strong lens-shading                                    | 11 |

| Figure 10: positive radial distortion (a: calibration pattern, b:barrel distortion, c: model)   | 12 |

| Figure 11: Backward mapping of output pixel positions into the input sampling grid              | 12 |

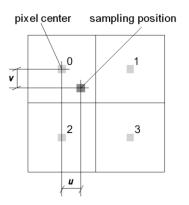

| Figure 12: Bilinear interpolation using 4 nearest neighbors                                     | 13 |

| Figure 13: Block diagram of a lens-distortion correction module for Xilinx FPGAs                | 14 |

| Figure 14: One dimensional resampling from 6 input to 5 output pixels                           | 15 |

| Figure 15: Example of a vertical scaling FIR filter stage, implemented using DSP48 primitives   | 15 |

| Figure 16: Example of a horizontal scaling FIR filter stage, implemented using DSP48 primitives | 16 |

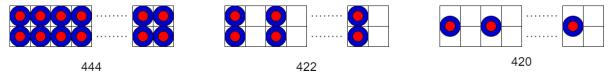

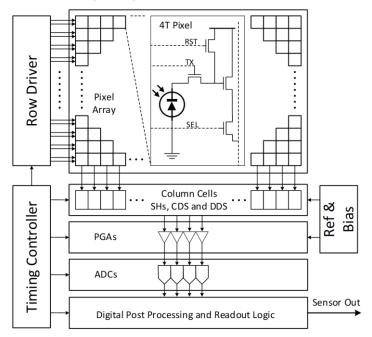

| Figure 17: YUV 444, 422, and 420 transmission and storage formats                               | 16 |

| Figure 18: NV12 component planes                                                                | 17 |

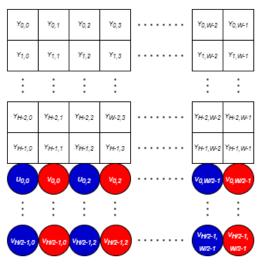

| Figure 19. Typical CMOS image sensor block diagram                                              | 18 |

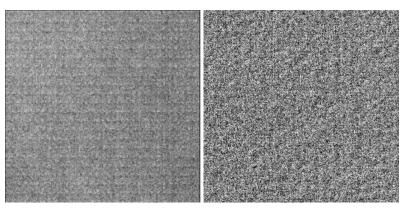

| Figure 20. FPN enhanced for visibility                                                          | 19 |

| Figure 21. Cone dataset original (left) and with FPN (right)                                    | 22 |

| Figure 22. Matching Density with (right) and without (left) FPN                                 | 22 |

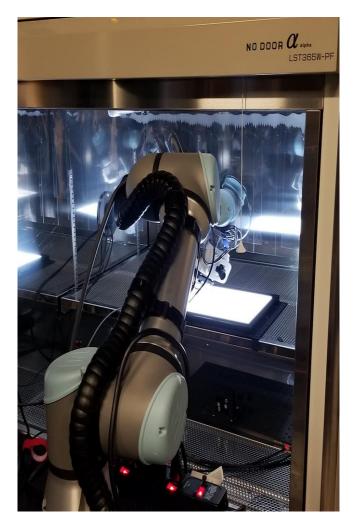

| Figure 23 Sensor assembly positioned by articulated robot arm in temperature chamber            | 24 |

| Figure 24. Static integrating sphere image artifacts                                            | 25 |

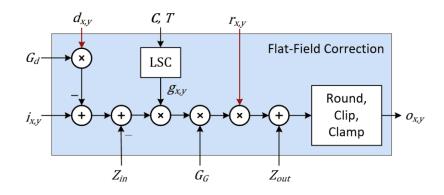

| Figure 25. Flat-Field Correction module block diagram                                           | 25 |

| Figure 26. Uniformity correction solution for stereo cameras                                    |    |

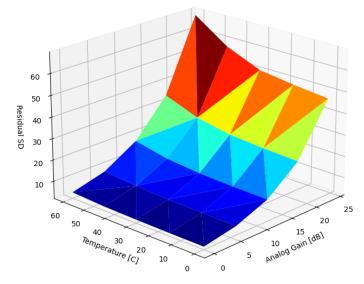

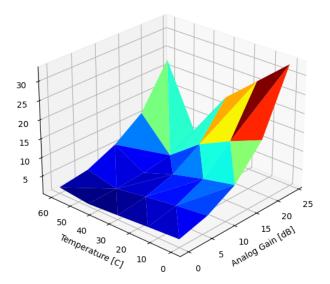

| Figure 27. Standard deviation of uncorrected DSNU                                               | 28 |

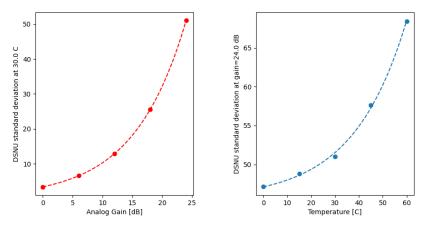

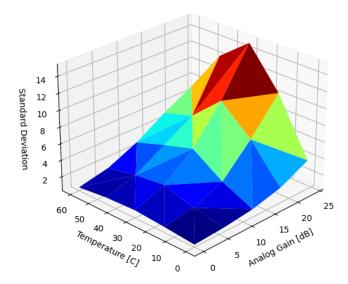

| Figure 28. SD of DSNU at 30°C (left), and at 24.0dB gain (right)                                | 29 |

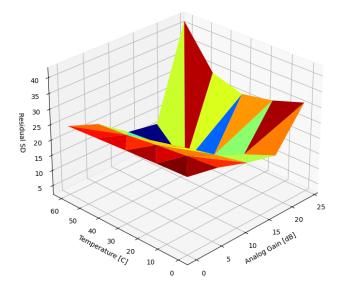

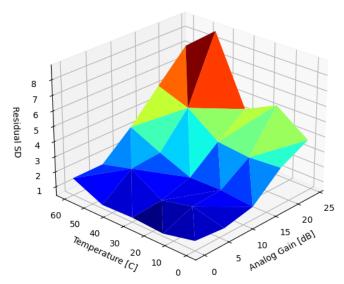

| Figure 29. SD of DSNU corrected with a single, static image                                     | 30 |

| Figure 30. Residual SD of DSNU with a single, scaled image                                      |    |

| Figure 31. SD of DSNU corrected with interpolated reference, using 4 reference captures         |    |

| Figure 32. SD of DSNU corrected with interpolation between 5 reference captures                 |    |

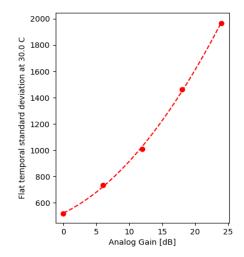

| Figure 33. SD of Shot noise as a function of analog gain ( $\alpha$ )                           |    |

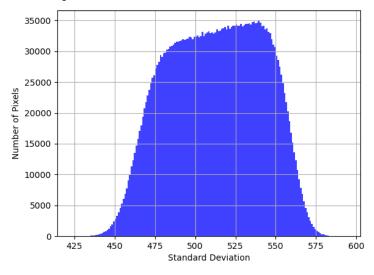

| Figure 34. Distribution of per-pixel SD at T=30°C, α=0.0dB                                      | 37 |

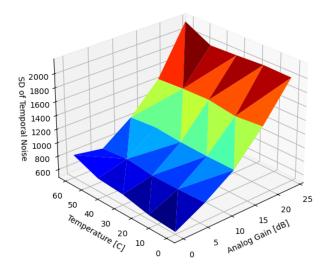

| Figure 35. Standard deviation of temporal noise $\sigma t(\alpha, T)$                           | 39 |

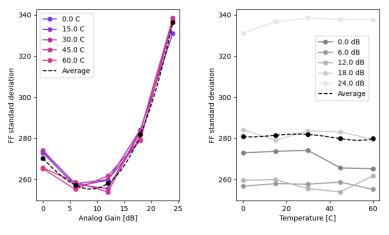

| Figure 36. Projections and averages of $\sigma r(\alpha, T)$                                    |    |

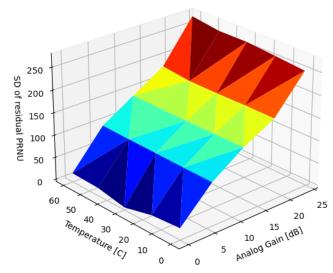

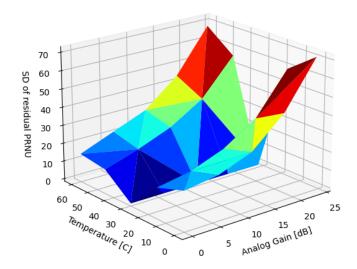

| Figure 37. Residual SD of PRNU, single reference correction                                     | 40 |

| Figure 38. Residual SD of PRNU, multi-reference correction                                      | 41 |

| Figure 39. Hybrid lens at 0°C corrected with 60°C image                                         | 41 |

| Figure 40. HIP of hybrid lens, 0°C corrected with 60°C                                          | 42 |

| Figure 41. HIP of LSC without de-center correction                                              | 43 |

| Figure 42. Example of a dead pixel in a sensor with Bayer                                       |    |

| Figure 43. Static solution for Stuck Pixel Correction                                           | 47 |

| Figure 44. | Nearest neighbors for Bayer CFA, and monochrome sensors                                     | 48 |

|------------|---------------------------------------------------------------------------------------------|----|

| Figure 45. | Simplified flow-chart of the proposed algorithm                                             | 49 |

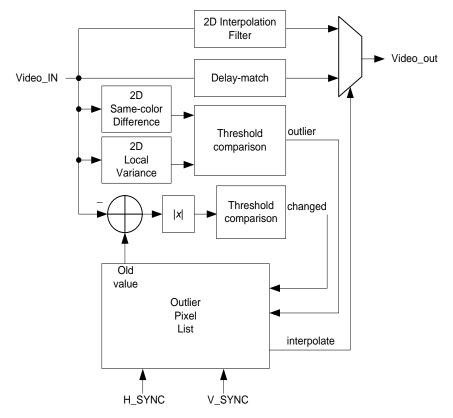

| Figure 46. | Block Diagram of an FPGA implementation                                                     | 50 |

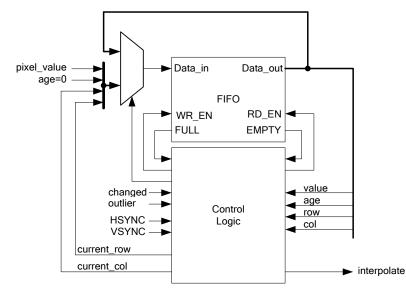

| Figure 47. | Block Diagram of an FPGA implementation                                                     | 51 |

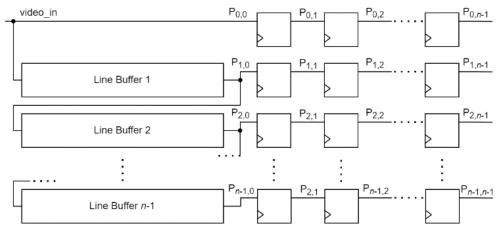

| Figure 48. | Input pixel matrix for the 2D interpolation kernel                                          | 52 |

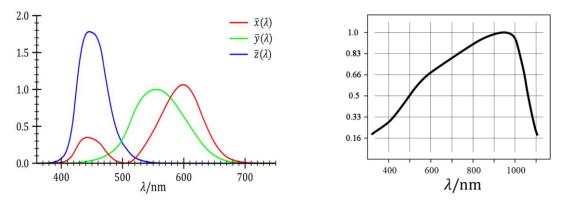

| Figure 49. | Normalized spectral responses of the CIE Standard Observer, and silicon photodiode          | 56 |

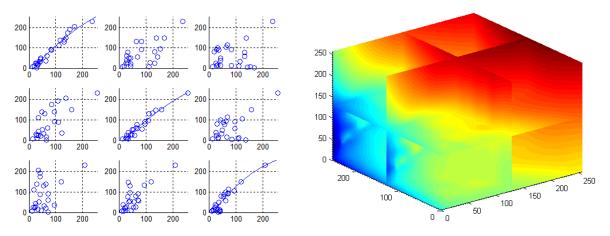

|            | RGB measured vs expected values (left: cartesian plot, right: R channel interpolation)      |    |

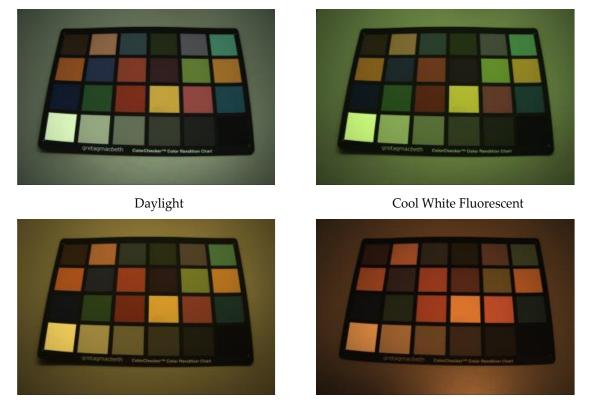

|            | Sensor images with different illuminants before lens correction                             |    |

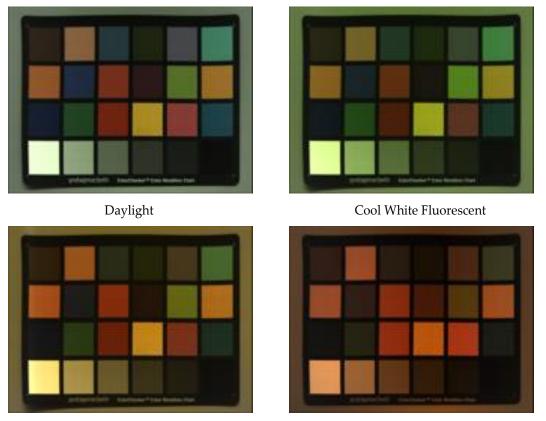

| Figure 52: | Lens corrected sensor images with different illuminants before color calibration            | 63 |

|            | Color Calibrated, lens corrected sensor images with different illuminants                   |    |

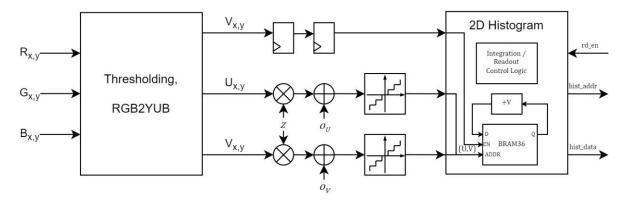

|            | Illuminator estimation specific hardware components in the Image Statistics ISP Module      |    |

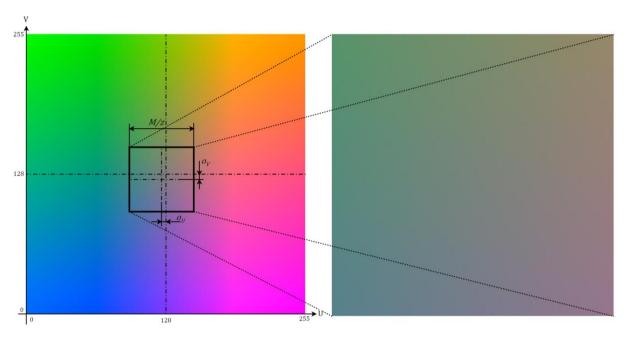

|            | U,V chrominance plane (left), zooming on the center region (right)                          |    |

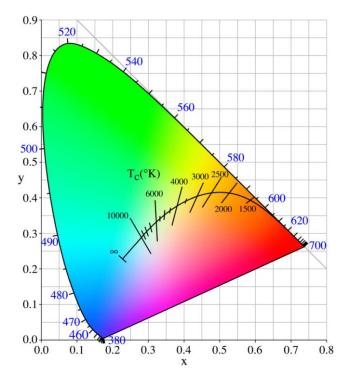

| •          | x and y coordinates of illuminants with different temperatures in CIE color-space           |    |

|            | Reference images with four different illuminators                                           |    |

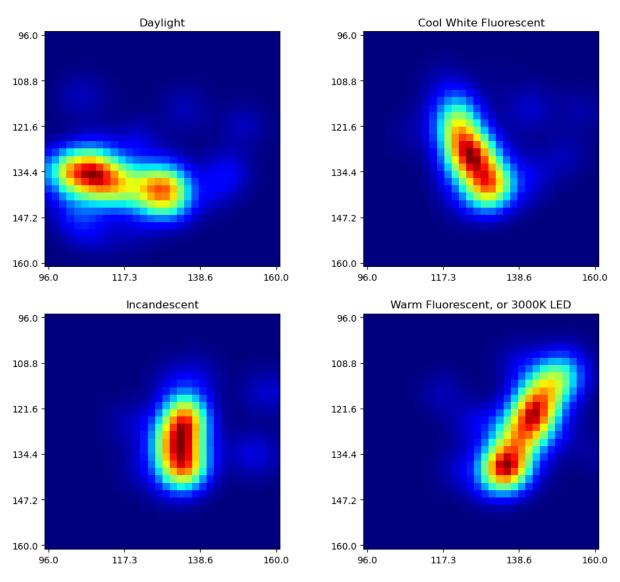

|            | averaged 2D UV histograms, $Hk(u, v)$ , with 4 different illuminants                        |    |

|            | Conference room image with dual illumination with AWB disabled (left), enabled (right)      |    |

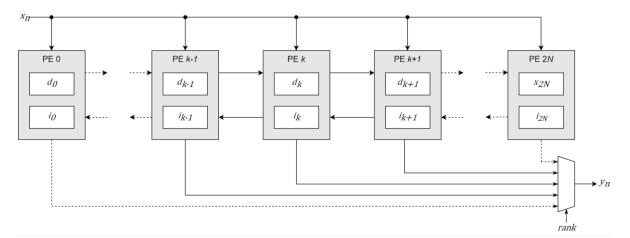

| •          | Block Diagram of a 1D rank-ordering architecture                                            |    |

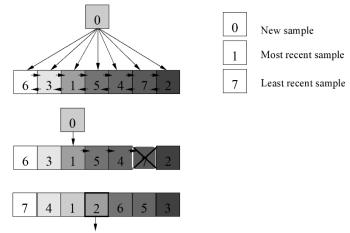

| 0          | Inserting a new sample to the magnitude ordered list                                        |    |

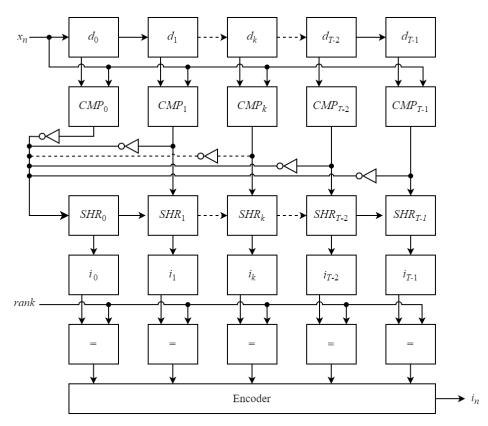

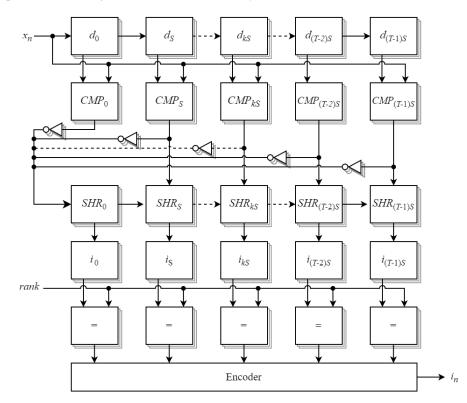

| 0          | Word-serial filter core architecture                                                        |    |

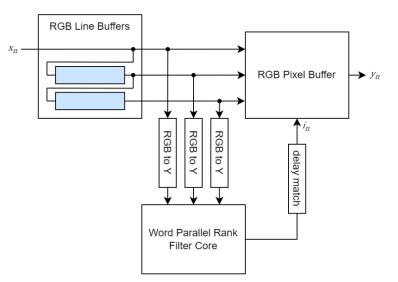

| 0          | Word parallel rank-filter architecture for RGB color image processing                       |    |

| 0          | Word-parallel filter core architecture                                                      |    |

|            | Virtual filter window with padding pixels                                                   |    |

| -          | Dedicated resources inserted into the logic fabric                                          |    |

|            | Loop-engine implementation                                                                  |    |

| 0          | Pipeline implementation                                                                     |    |

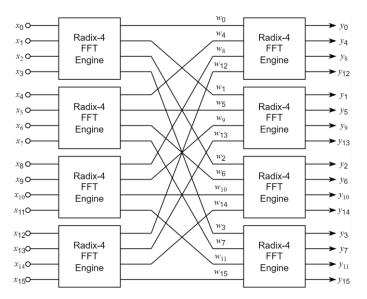

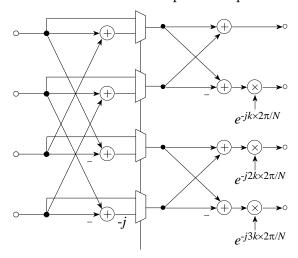

| •          | 16 point, radix-4 FFT                                                                       |    |

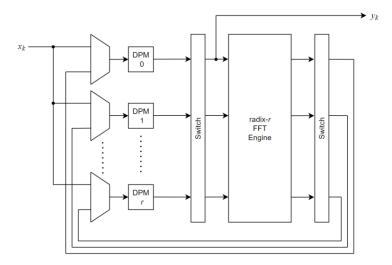

| 0          | Single buffer Radix-4 FFT loop engine                                                       |    |

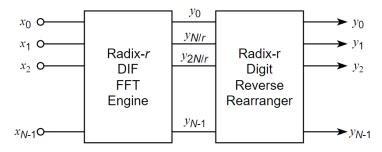

| -          | Radix <i>r</i> DIF FFT with data reorganizer                                                |    |

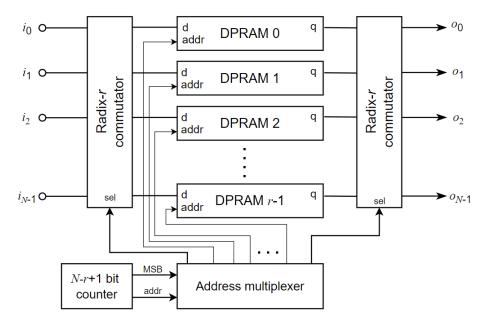

| 0          | Example of a <i>r</i> input, <i>r</i> -output, data reorganizer for radix- <i>r</i> FFTs    |    |

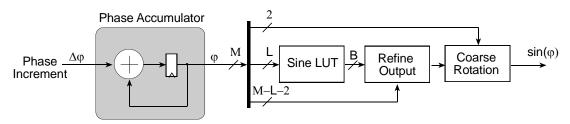

| 0          | Typical DDS block diagram                                                                   |    |

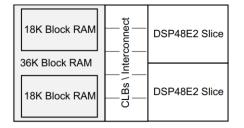

|            | Xilinx Ultrascale BRAM, CLB and DSP48 slice tile                                            |    |

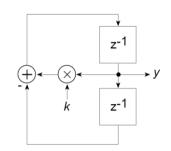

|            | Two-pole resonator                                                                          |    |

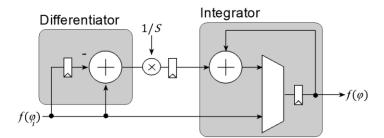

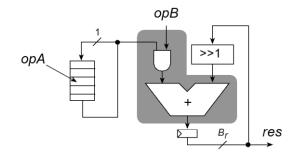

| •          | DI structure with preload                                                                   |    |

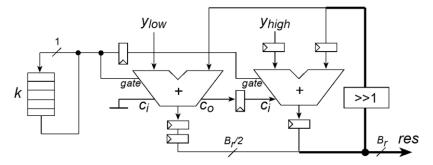

| e          | DDII structure                                                                              |    |

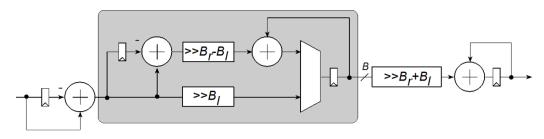

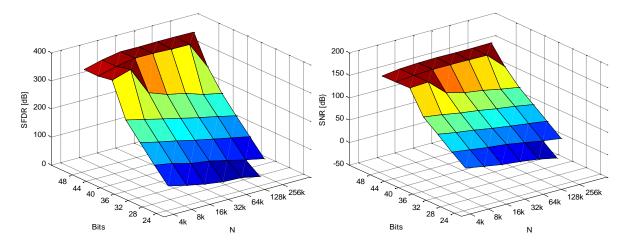

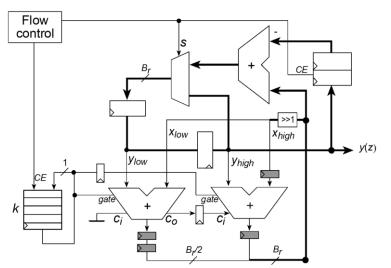

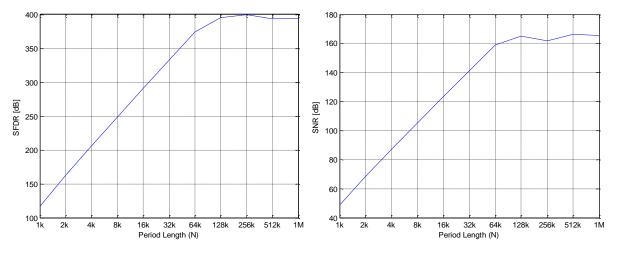

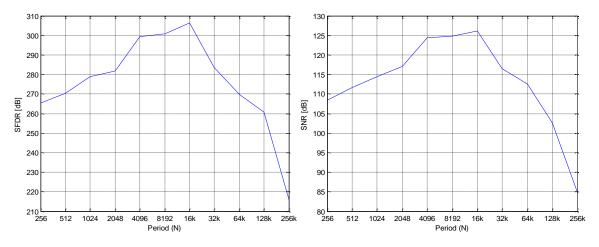

| 0          | SFDR (left) and SNR (right) as a function of <i>N</i> and <i>B</i> , <i>M</i> =128          |    |

| 0          | Bit-serial multiplier                                                                       |    |

| 0          | Pipelined bit-serial multiplier                                                             |    |

|            | Pipelined bit-serial resonator                                                              |    |

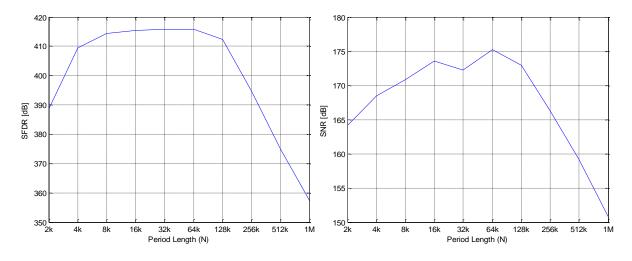

| 0          | SFDR (left), and SNR (right) for the resonator + quadratic interpolator, as a function of N |    |

| 0          | Pipelined adder / subtractor                                                                |    |

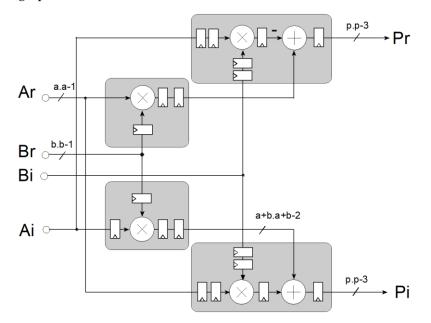

| •          | Complex multiplier with 4 real multipliers                                                  |    |

| 0          | Complex multiplier with 3 real multipliers                                                  |    |

|            | Block diagram of a Color Filter Array Interpolator                                          |    |

|            | Butterfly operation                                                                         |    |

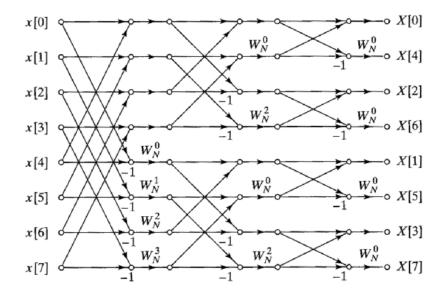

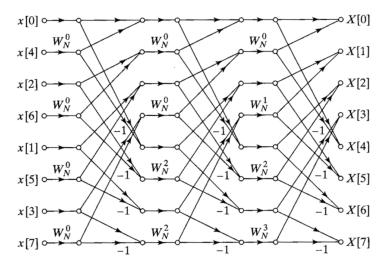

|            | Eight point DIT FFT                                                                         |    |

|            | Eight point DIF FFT                                                                         |    |

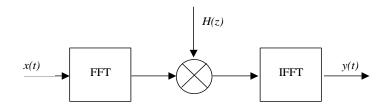

|            | Cyclic Convolution in the Frequency Domain                                                  |    |

| -          |                                                                                             |    |

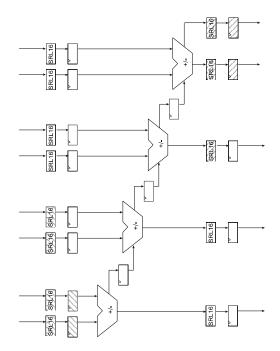

| Figure 92. FFT architecture with similar stages                                                        | 111 |

|--------------------------------------------------------------------------------------------------------|-----|

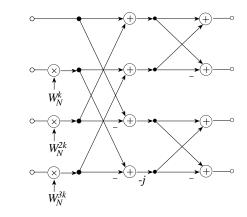

| Figure 93. Radix-4 DIT dragonfly                                                                       | 112 |

| Figure 94. Radix-4 PE with bypass-option                                                               | 116 |

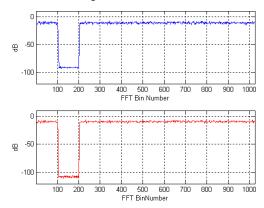

| Figure 95. FFT Dynamic range (N=1024, blue: 18-bit fixed-point, red: double precision)                 | 118 |

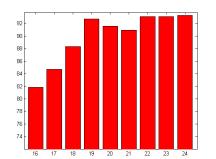

| Figure 96. Dynamic range as a function of fractional bits carried                                      | 119 |

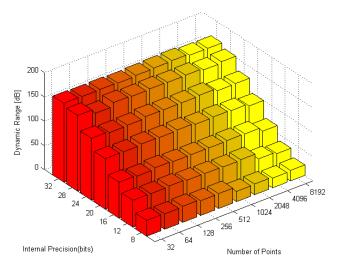

| Figure 97. FPR dynamic range as a function of transform size (N) and internal precision                | 119 |

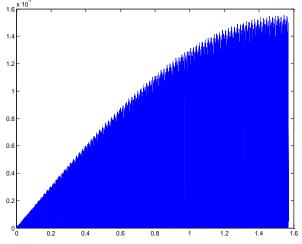

| Figure 98. 1407 point linear interpolation, time domain error                                          | 121 |

| Figure 99. Constrained Multiplier                                                                      | 124 |

| Figure 100. Pipelined resonator using block multipliers                                                | 125 |

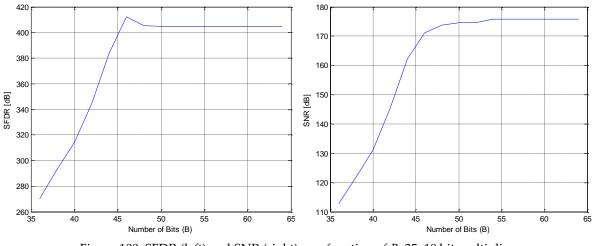

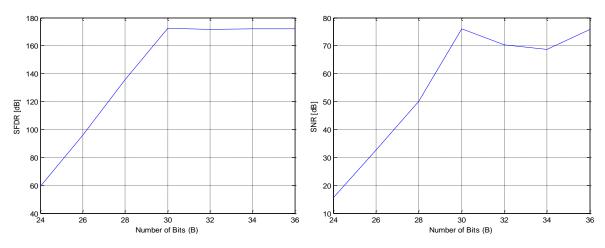

| Figure 101. SFDR (left) and SNR (right) as a function of <i>B</i> , 35x18 bit multiplier               | 126 |

| Figure 102. SFDR (left) and SNR (right) as a function of <i>B</i> , 18x18 bit multiplier               | 126 |

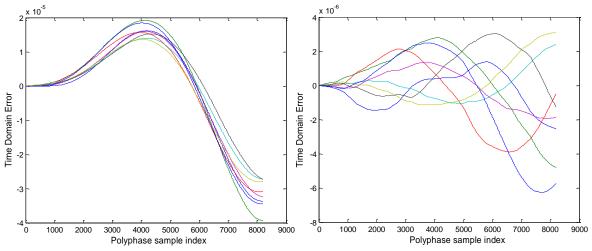

| Figure 103. Time Domain error without (left) and with (right) frequency dithering, $N = 216$ , $p = 8$ | 127 |

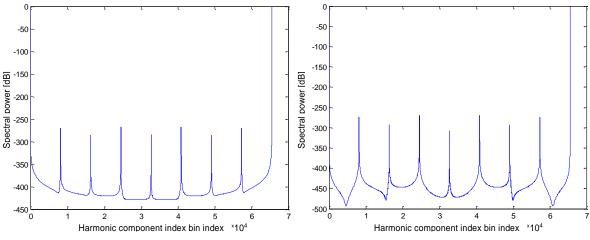

| Figure 104. Output spectrum [dB] without (left) and with (right) frequency dithering                   | 127 |

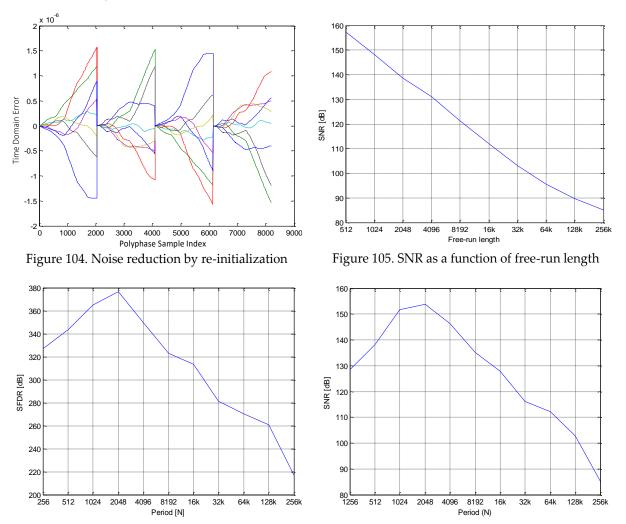

| Figure 105. Noise reduction by re-initialization                                                       | 128 |

| Figure 106. SNR as a function of free-run length                                                       | 128 |

| Figure 107. SFDR (left) and SNR (right) as a function of N (35x18 bit multiplier)                      | 128 |

| Figure 108. Resonator structure with re-initialization support                                         | 129 |

| Figure 109. Amplitude errors of <i>p</i> =8 phases                                                     | 130 |

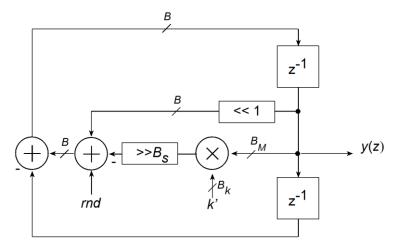

| Figure 110. Modified $\Delta\Sigma$ converter                                                          | 131 |

| Figure 111. Amplitude errors of <i>p</i> =8 sub-processes                                              | 131 |

| Figure 112. SFDR (left) and SNR (right) as a function of N, 18x18 bit multiplier                       | 131 |

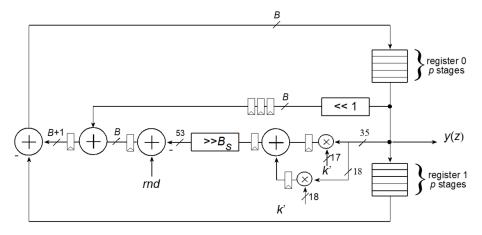

| Figure 113. Phase factor source for in-place FFTs based on DII structure                               | 132 |

| Figure 114. SFDR (left) and SNR (right) of the quadratic interpolator as a function of N, B=36, M=1024 | 134 |

## **List of Tables**

| Table 1: DSNU Standard Deviation and Pearson correlation                                        | 28  |

|-------------------------------------------------------------------------------------------------|-----|

| Table 2: SD and Pearson correlation with static reference                                       | 30  |

| Table 3: Residual SD, Pearson correlation, DSNU reduction using interpolation with 5 references | 34  |

| Table 4: FF Standard Deviation and Pearson correlation                                          | 36  |

| Table 5: SD of PRNU and residual, single reference correction                                   | 40  |

| Table 6: Output of adder stages based on input validity                                         | 53  |

| Table 7: Performance and resource use for Xilinx FPGAs, method (A)                              | 54  |

| Table 8. Characterization of color correction methods                                           | 57  |

| Table 9. Maximum word-serial processing frequencies, 24bit RGB processing                       | 80  |

| Table 10. Approximate LUT usage for 3x3, 5x5, and 7x7 configurations                            | 80  |

| Table 11. Data accesses, radix-4 FFT engine, N=16                                               | 82  |

| Table 12. Static memory segmentation for $N = 64$ , $r = 4$                                     | 84  |

| Table 13. Static memory segmentation for $N = 32$ , $k = 4$ , $k'=2$                            | 85  |

| Table 14. Multiplier usage by point-size and FFT implementation type (16 bit precision)         | 87  |

| Table 15. BRAM usage by point-size and FFT implementation type (16 bit precision)               | 87  |

| Table 16. Slice usage by point-size and FFT implementation type (16 bit precision)              | 87  |

| Table 17. Transform times [us] as a function of architecture and point-size[N]                  | 87  |

| Table 18. Reduction in BRAM allocation compared to naïve double-buffered implementation         | 88  |

| Table 19. Algorithmic Techniques (Memory Compression and SFDR).                                 | 98  |

| Table 20. sample ordering per FFT configuration                                                 | 110 |

| Table 21. Multiplier counts for different radixes                                               | 113 |

| Table 22. Comparison of computational requirements                                              | 114 |

## **1** Introduction

Logic will get you from A to B. Imagination will take you anywhere. — Albert Einstein

#### 1.1 Field Programmable Gate Arrays

A Field Programmable Gate Array (FPGA) is an array of configurable logic blocks (CLB) connected by programmable routing on a single silicon device [1]. The logic blocks contain a combinatorial unit, usually implemented as a small Static Random Access Memory (SRAM) component, a set of registers, logic gates and multiplexers to support typical computation tasks such as carry logic.

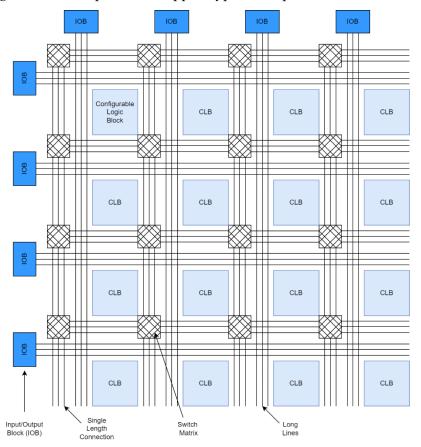

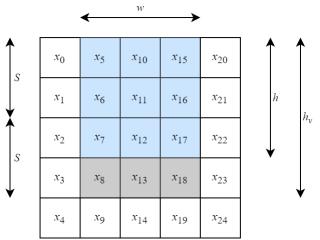

Figure 1: Simple Sea of Gates FPGA architecture.

Configuration of CLBs allow implementation of basic logic gates as well as more complex logic functions such as arithmetic operators, multiplexers, decoders, or state machines. Programmable, hierarchical routing via switch matrixes allows cells to communicate with each other and the Input/Output blocks which connect the programmable network to external components, memories, processors, etc. All operations take place simultaneously across the whole array, synchronized by dedicated, low-skew, high fanout clock routing to all cells. The architecture of a simple, Sea-of-Gates FPGA is illustrated on Figure 1.

#### 1.1.1 Evolution and Structure

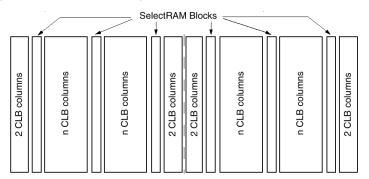

In the early 2000s, CLBs were combined to slices, and devices were segmented into an array of tiles. More complex blocks, such as 18kbit RAM blocks (BRAM), and 18x18 multipliers were embedded between the tiles. Next 18x18 block multipliers were augmented with wide accumulators to reduce the implementation footprint of typical DSP operations. In the past decade, processor cores, external memory interfaces, and hardened peripherals (I2C, SPI, UART) were embedded into the configurable array leading to the latest heterogenous multiprocessing System-on-a-Chip (SoC) platform [2],[3].

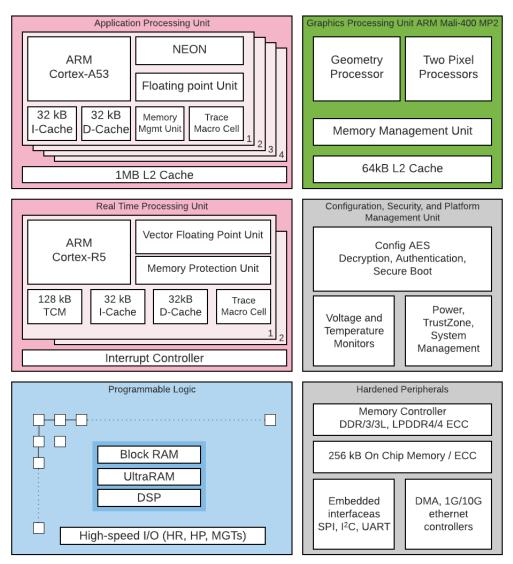

Figure 2: Example block diagram of a modern FPGA device<sup>1</sup>.

The latest generation of FPGA devices, such as the Xilinx Zynq Ultrascale+ MPSoC (Figure 2), include multicore, heterogenous processing system (PS), GPUs, and various hardened functions, such as Memory and Network controllers, peripherals, such as I2C, SPI controllers, DMA and watchdog timers. Thousands of DSP engines with single precision floating point units with integrated hierarchical cache memories can implement complex, high performance video processing solutions. Beyond implementing SIMD or MIMD architectures, fine grain

<sup>&</sup>lt;sup>1</sup> Source: adapted from <u>https://www.xilinx.com/products/silicon-devices/soc/zynq-ultrascale-mpsoc.html</u>

configurability enables FPGAs to implement custom DSP and image processing blocks, allowing multiple trade-offs between area, performance, and numerical precision.

Early use of FPGAs as a derivative of Complex Programmable Logic Devices (CPLD) was gluelogic between system components. With relentless miniaturization and specialization, modern devices have the capacity and features to implement complex machine vision algorithms [4],[5]. FPGAs are increasingly used in high performance computing applications either as the sole central computing element or as a coprocessor. As a dedicated peripheral, or custom, reconfigurable accelerator, FPGAs can execute digital signal processing (DSP) operations such as convolutions, pixel level image processing such as edge detection, or perform Convolutional Neural Network (CNN) inference. The latest generation of FPGAs can implement thousands of single precision floating point units, which can compute a result every single clock cycle. This flexibility allows trading numeric precision for an increased number of parallel arithmetic units.

Segments of a physical part can work at different clock rates matched to source synchronous data rates. The inherent parallelism of logic resources on an FPGA enables the implementation of high throughput custom hardware accelerators, high-bandwidth custom DSP or video processing equipment.

#### 1.1.2 Design Entry and Configuration

CLBs and routing are configured by programmable switches. Several technologies are used to implement these programmable switches, which is one of the technological factors determining the density and versatility of the resulting network. Fuse or anti-fuse based programming technology allocates minimal footprint for switches, but the resulting structure is one-time programmable. SRAM based configuration switches allocate more silicon area but are reprogrammable. Flash based devices are reprogrammable and retain configuration content during power-down.

Programmable routing, slice, and hard macro configuration, as well as memory initialization for the PS, is carried out via configuration files. Configuration files are generated by vendor specific back-end tools. On the front-end of the toolchain the user specifies the design in the form of schematics, Hardware Description Language (HDL) description, or using higher level programming languages such as of C++ or MATLAB code. Synthesis translates the design to a netlist of logical operators, which subsequently got mapped to the logic resources offered by the target FPGA. Finally, the mapped design needs to be placed and routed in such that the resulting network of interconnected components meet timing specifications.

### 1.2 Signal and Video Processing

One application area of FPGAs is rapid prototyping of integrated circuits. With the FPGA manufacturer taking the costs, risks, and complexities of silicon design and fabrication, users can take advantage of novel process nodes and transistor densities while paying a higher price for each device. FPGAs are the final implementation solution for high-cost, low-volume products requiring custom high speed signal processing. Prime examples are airborne and maritime radar, high security IP networks and early deployments of cell phone base stations. In these application areas FPGAs perform Digital Signal Processing (DSP) operations such as

- baseband signal processing: filtering, enhancement, reconstruction,

- compression, decompression, encryption, decryption, error detection and correction,

- modulation, demodulation, up-, and down conversion,

- Multiple Input Multiple Output (MIMO) beamforming,

- channel equalization

Another area of widespread FPGA adoption is custom video equipment. Professional video capturing-, recording-, and processing equipment, airborne and military camera systems, high resolution, and high frame scientific cameras can carry the cost and power requirements of FPGA based computing.

Most high level signal and video processing algorithms use a few basic building blocks, such as:

- 1D and 2D correlations and convolutions,

- array thresholding, minimum-, and maximum calculation, normalization,

- Finite Impulse Response (FIR) and Infinite Impulse Response (IIR) filters,

- Fast Fourier, Discrete Cosine and Wavelet transforms,

- Data interleaving, indexing and reorganization.

An FPGA SoC may be the sole processing module in a system, but often FPGAs are used in conjunction with higher density, specialized processing modules. Based on the nature and complexity of the signal processing problem, architects have several options to balance cost, power, and complexity. Problems with low to moderate computational complexity can be addressed by single processor systems. Computationally intensive applications may need multi-core systems, or a General Purpose CPU extended with GPUs, Neural Network inference engines, or specialized hardware accelerators. One particularly attractive, low cost way to increase performance is the use of FPGA based hardware accelerators. This paradigm is in the focus of major processor manufacturers, underscored by a string of acquisitions by large processor manufacturers, such as Altera (now part of Intel)<sup>2</sup>, Xilinx (now part of AMD)<sup>3</sup> and Atmel (now part of Microchip)<sup>4</sup>.

Appendix A.1 reviews concepts and limitations of GP/GPU systems collocated in modern FPGA based SoCs, as well as the basic DSP operations and their optimizations in FPGAs.

<sup>&</sup>lt;sup>2</sup>https://www.intel.com/content/dam/www/central-libraries/us/en/documents/agilex-fpgas-game-changing-white-paper.pdf

<sup>&</sup>lt;sup>3</sup> <u>https://www.xilinx.com/support/documentation/data\_sheets/ds891-zynq-ultrascale-plus-overview.pdf</u>

<sup>&</sup>lt;sup>4</sup> https://www.microchip.com/en-us/products/fpgas-and-plds/system-on-chip-fpgas/polarfire-soc-fpgas

# 2 Image Signal Processing

FPGAs are ideal for implementing demanding image and signal processing algorithms due to the inherent parallelism of logic resources. Recognition, registration, and reconstruction all need consistent, high-quality images [6]. The purpose of Image Signal Processing (ISP) is to condition images for higher level processing functions. As opposed to other machine vision platforms, such as GPGPU SoCs, like the Nvidia Xavier AGX<sup>5</sup>, specialized ASICs, like the Intel Movidius Myriad<sup>6</sup>, or mobile platforms, like the Qualcomm Snapdragon 865<sup>7</sup>, FPGAs do not currently have hardened ISP units. While embedded ASSPs have dedicated, proprietary image sensor processing pipelines, FPGAs offer PL resources, tightly integrated with a system processor (PS).

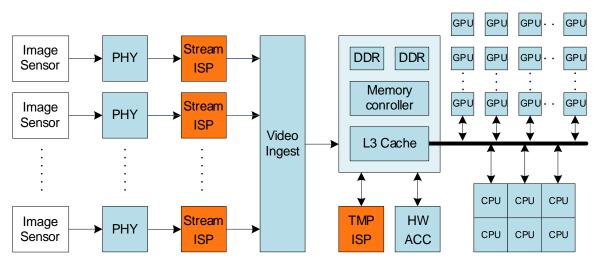

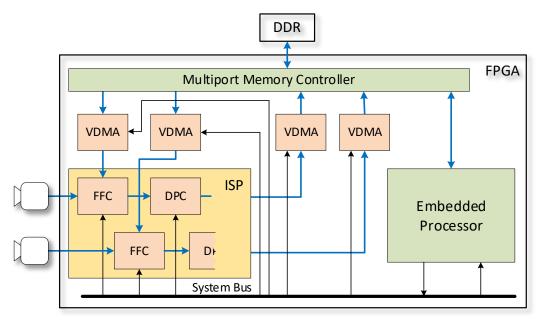

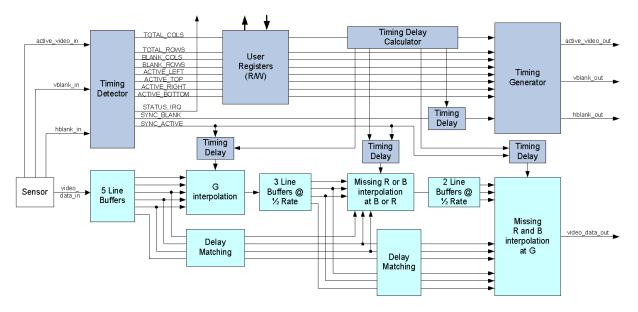

Figure 3: Example implementation of a machine vision platform

Figure 3 presents a typical machine vision platform, with one-, or multiple image sensors providing input to processing algorithms executed on an array of GPU and CPU cores. Image sensors typically connect to the platform via MIPI CSI2.0 DPHY or CPHY, sLVDS, SLVS-EC, or parallel CMOS interfaces. FPGAs provide high-speed I/O features to receive, de-serialize, and deinterleave streams, performed by the PHY blocks on Figure 3.

Spatial ISP functions can be performed directly on the image streams, without having access to previous frames. A Streaming ISP pipeline block can perform:

- Flat-field and pixel defect correction,

- Lens shading correction,

- Bayer Color Filter Array (CFA) interpolation,

- Spatial edge enhancement and noise removal,

- Color correction and Tone mapping,

- Video format conversion (chroma resampling, video scaling)

<sup>&</sup>lt;sup>5</sup> <u>https://www.nvidia.com/en-us/autonomous-machines/embedded-systems/jetson-agx-xavier</u>

<sup>&</sup>lt;sup>6</sup> <u>https://www.intel.com/content/www/us/en/products/sku/204770</u>

<sup>&</sup>lt;sup>7</sup> <u>https://www.qualcomm.com/media/documents/files/qualcomm-snapdragon-865-5g-mobile-platform-product-brief.pdf</u>

Received frames are subsequently stored in video frame buffers, and are made available to a second set of ISP functions, performing functions using the frame buffer such as:

- Motion adaptive temporal noise reduction,

- Image composition,

- Geometry correction, de-warping, rotation and/or translation

- Frame rate changes or High-dynamic-range (HDR) processing,

which are dependent on accessing multiple video frames at a time.

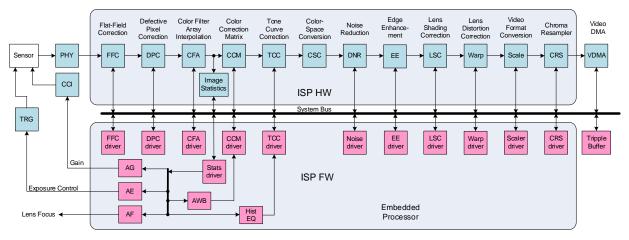

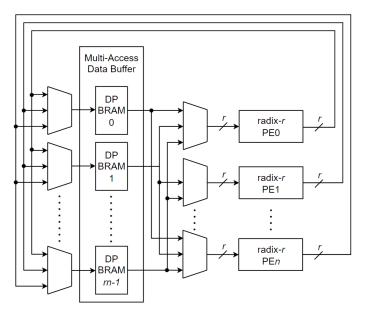

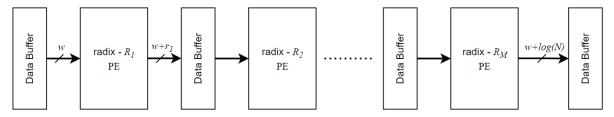

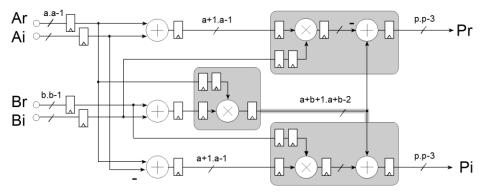

Figure 4: Streaming ISP pipeline HW and FW components

Figure 4 illustrates a typical streaming ISP pipeline, with blue functional units implemented in FPGA PL as custom accelerators, with corresponding drivers and low-level ISP functions (pink blocks) implemented as Firmware (FW), executed by the SoC PS. The camera-side interface of the image sensor processor receives the sensor pixel stream via Physical (PHY) interface module, which de-serializes high speed transmission formats to parallel video data.

#### 2.1 Flat-Field Correction

Flat-field Correction (FFC) aims to remove fixed-pattern image artifacts introduced by the nonuniformities of the sensor and/or the optical system. FFC allows correction of:

- Dark Signal Non-Uniformity (DSNU), pixel-to-pixel differences in dark current,

- Photo Response Non-Uniformity (PRNU), pixel to pixel sensitivity differences,

- vignetting or lens shading,

- other optical defects, such as scratches or contamination of the optical system.

For assessing DSNU, a set of reference images are collected with no exposure – often with the sensor covered [7]. For PRNU, a large set of reference images with uniform illumination are captured and combined into a single frame referred as the flat frame [8].

Due to the characteristic, row/column separable nature of DSNU and PRNU, for high-resolution cameras high-frequency pixel to pixel correction is often performed by row and column projections of calibration images [9]. In this case, lens-shading correction is performed by a separate ISP module based on a parametric vignetting model of the optical system. For systems where access to a compressed, or uncompressed calibration frame is feasible, pixel to pixel compensation can be applied. The flat-field corrected image can be given formally as:

$$I_{FFC} = \frac{I - I_D}{I_F - I_D} m - c, \tag{1}$$

where *I* is the input image to be corrected,  $I_D$  is the dark calibration image,  $I_F$  is the flat calibration image, and *m* and *c* are constants to adjust the output brightness and black level, respectively. My work on the field of Flat-Field correction is detailed in Chapter 3.

### 2.2 Defective Pixel Correction

An image sensor may have defects by the linear correction capabilities of the FFC module, affecting individual pixels, or clusters. Affected pixels may have significantly altered dark currents (hot pixels), sensitivities (dead pixels), or excessive noise load (flickers)<sup>8</sup>. Sensors failing image quality checks are discarded by manufacturers. Most defects affecting machine vision systems arise during use by high energy particles impacting photodiodes. The purpose of defective pixel correction (DPC) is the identification and interpolation of these defective pixels.

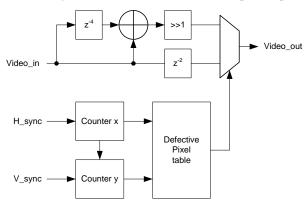

In static solutions, locations of defects outside the range correctable by FFC are identified during FFC calibration and are stored in a Look-Up-Table. During regular operation sensor images are not analyzed for defective pixels, but defective pixel locations are interpolated on the fly.

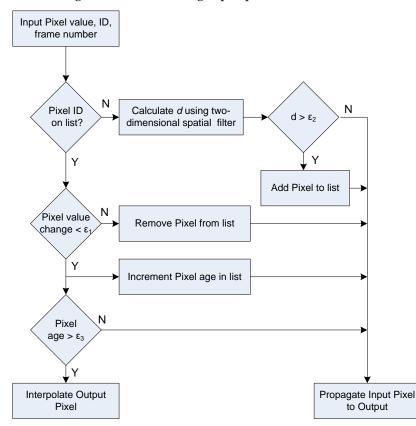

Dynamic solutions analyze the sensor data stream for outlier pixels, which are apparently stuck or flicker independent of local motion and neighboring pixel values. While dynamic solutions are significantly more complex and often require access to frame buffers, they can keep up with the degradation of the sensor due to the detection of accumulating pixel defects. My work on the field of DPC is detailed in Chapter 4.

### 2.3 Color Filter Array Interpolation

Color image sensors use a color filter matrix, laid over the photodiode array, so adjacent, uniform photodiodes can have different spectral sensitivities. The Bayer Color Filter Array (CFA) is the most commonly used arrangement of color mosaic filters, using Red, Green, and Blue (RGB) or Cyan, Magenta and Yellow (CMY) dyes (Figure 5). The mosaic pattern is laid out in repeating lines.

| G | R | G | R | Y | М | Y | М |

|---|---|---|---|---|---|---|---|

| В | G | В | G | С | Υ | С | Y |

| G | R | G | R | Y | М | В | М |

| В | G | В | G | С | Y | С | Y |

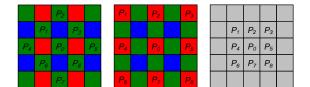

Figure 5. Examples of the Bayer RGB Color Filter Array pattern (left: RGB, right CMY)

From one measured color component per pixel, the Bayer CFA interpolation module restores 3 color components per pixel, using information from the neighboring pixels. The pigments used in the color filters absorb some spectral components of incident light, reducing pixel sensitivity and quantum efficiency. With the green filter most translucent and most similar to human perception of luminance, the array contains twice as many green pixels than red or blue pixels. The CFA subsamples the image digitized by the sensor, which may introduce color aliasing effects, if the region interpolated contains spectral components between the spatial sampling frequency of the pixel array  $f_M = 1/D$ , the sampling frequency of the color channels  $f_{R,B} = 2/D$ , where *D* is the pixel size.

<sup>8</sup> The International Standard on Ergonomic Image Quality Requirements, pp 2-3: <u>https://standards.iteh.ai/catalog/standards/cen/346aee7a-22c1-466a-9acf-622f79ee1937/en-iso-13406-2-2001</u>

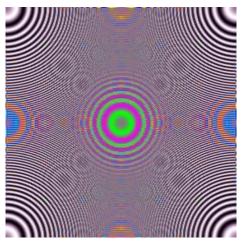

Simple bilinear interpolation with constant weights may introduce severe color artifacts, as illustrated by zoneplate image (Figure 6, left), which represents a 2D spatial frequency sweep from the corners (low frequencies) to the center (high frequencies).

The right side image of Figure 6 shows an excerpt of the light house test image, demonstrating suppressed color artifacts on the natural horizontal frequency sweep of the picket fence.

Figure 6. Examples of CFA interpolation color artifacts (left: Zoneplate, right: Lighthouse<sup>9</sup>)

Details on my work on the field of FPGA optimized CFA interpolation and post-processing have been presented in section A.2 of the Appendix and were published in [S1].

### 2.4 Image Statistics

The Image Statistics module implements the computation intensive metering functionality common in digital cameras and imaging devices. Collecting data on a per pixel basis is in many cases prohibitively expensive using ASSPs. Statistical data is consumed by Automatic Exposure (AE)-, Gain (AG), Focus (AF), and White Balance (AWB) control as well as tone curve correction algorithms. The module collects global statistical information over the entire image frame, such as a global histogram, which can be used for tone map correction. Automatic Exposure Control (AE), Automatic White Balancing (AWB), and Automatic Focus (AF) adjustment, often referred to as "3A" algorithms, often rely on local, zone based information, often referred to as zone based metering. High-, and low-frequency, or edge content in considered for adjusting focus, local mean, minimum, maximum, and histograms are used to control exposure and gain. The statistics module analyzes the pixel stream passing through the module, and deposits data either as in ancillary video lines, or metadata corresponding to the frame.

### 2.5 Color Correction Matrix

The color correction matrix (CCM) is a 3x3 programmable coefficient matrix multiplier with offset compensation that can be used to adjust color component gains, mix-, or decorrelate color channels, adjust zero offset, or convert between color spaces. The 9 coefficients for the 3x3 multiplier, and the 3 coefficients for the output channel offsets can be re-programmed on a frame-by-frame basis. The CCM is the actuator for AWB, controlled by the SW component of the AWB algorithm.

<sup>&</sup>lt;sup>9</sup> Source: Kodak Lossless True Color Image Suite, image#19 by Alan Fink, Eastman Kodak Company

The physical implementation of this module uses 9 DPS48 tiles, which can perform the matrix multiplication, offset compensation, and unbiased rounding using 24 bit coefficients on 8-18 bit color channels.

#### 2.6 Tone Curve Correction

The tone mapping module can implement arbitrary one-dimensional functions specific for a color channel. Typical use cases include gamma correction, logarithmic encoding, or mapping from 10,12 or higher input color-depth to 8-bit color representation, typical to consumer displays. Tone curves can be re-programmed on a frame-by-frame basis. The tone-curve module is the actuator for histogram equalization, and for the adaptive histogram equalization / CLAHE algorithm [10].

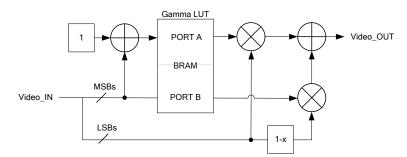

Figure 7: 12 bit gamma correction module with interpolation

BRAM primitives can store 1024x18 bits, and map 10 bit inputs to up to 18 bit outputs. For input color channels with more than 10 bit resolution, the interpolator illustrated on Figure 7 can be used. The desired mapping function f(s) can be interpolated by  $\hat{f}(s)$  by splitting the bits of the input sample as  $s = (y \ll k) + x$ , where x represents the k LSBs:

$$f(s) \approx \hat{f}(s) = f(y)(1-x) + f(y+1)x$$

(2)

The 10 most significant bits of the input (y) are used to address the dual-ported BRAM and fetch corresponding values f(y) and f(y + 1). The lower k LSBs are used to interpolate between the two nearest mapping function values f(y) and f(y + 1).

#### 2.7 Color-Space Conversion

A color space is a numerical representation of colors. The most popular color models are:

- RGB, and gamma corrected R'G'B', used in computer graphics,

- YIQ, YUV, YCrCb used in video systems,

- CMYK used in color printing,

- CIELAB, CIEXYZ, designed to represent colors the average human can see,

- HSV (Hue, Saturation, Value) and HSL (Hue, Saturation, Luminance).

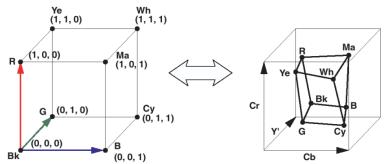

HSV and HSL are related to the intuitive notions of hue, saturation, and brightness. Representation in one color space can be transformed to another using appropriate mapping functions. Native input to the conversion is typically the RGB information supplied by devices such as cameras and scanners. Conversion from RGB to YUV/YCrCb (Figure 8) is a typical operation transforming sensor input pixels to industry standard video transport formats, such as YUV 422 and YUV420. The color-space conversion module simplifies the 3x3 linear transformation between input and output color channels and uses only 4 multipliers and 5 adders to carry out the computations.

Figure 8: Conceptual conversion between the RGB and YCrCb color-spaces<sup>10</sup>

#### 2.8 Noise Reduction

Images in video-, or image sensor streams can be corrupted by noise. The three most common sources of noise are shot noise, thermal noise (analog electronic interference with Gaussian distribution can also be modeled as thermal noise), and salt-and-pepper noise, which is due to occasional bit-flips during serial transmission. According to the central limit theorem, the aggregate of statistically independent shot noise instances captured by pixels converge to a Gaussian distribution over the entire image. Salt-and-Pepper noise can be effectively combated by 2D non-linear filtering. My work on the field of efficient FPGA implementation of 2D rank-, and median filters is expanded in Chapter 6. A brief summary of common methods to suppress Gaussian noise is provided in Appendix section A.2.4.

#### 2.9 Edge Enhancement

Enhancement of features, such as edges and contours, is a typical image pre-processing operation, improving not only the visual appearance of captured images but the accuracy and performance of downstream recognition and classification tasks [11]. Simple approaches like Prewitt and Sobel edge detectors produce predictable results, but are sensitive to noise, distort texture and unlikely to connect broken edges. Robust algorithms often rely on context from image pyramids or persistence of features across multiple image frames. However, these pre-processing features are seldom available for streaming ISPs. I proposed an edge enhancement and spatial noise suppression solution suitable for FPGA / ASIC implementation [S1], [S2], based on approximation of local edge orientation and strength based on edge detection and morphological operations. The proposed architecture used steerable edge enhancement and blurring kernels. Blurring kernels were used on smooth image areas with low edge strength to reduce noise. Edge enhancement kernels were oriented perpendicular to detected edges. Edge enhancement of features in the presence of noisy input continues to remain an area of active research.

### 2.10 Lens Shading Correction

Lens shading, or vignetting, is the progressive darkening of image content from the center towards the corners of the image due to optical-, physical-, and pixel vignetting. Optical vignetting is caused by the lens entrance aperture, which limits the amount of light reaching the sensor. Optical

<sup>&</sup>lt;sup>10</sup> Source: RGB to YCrCb Color-Space Converter v7.1, LogiCORE IP Product Guide, Xilinx Vivado Design Suite, PG013. <u>https://docs.xilinx.com/v/u/en-US/pg013\_v\_rgb2ycrcb</u>

vignetting is proportional to  $\cos^4 \theta$ , where  $\theta$  is the incident angle relative to the optical axis of the lens system. Physical vignetting occurs when other mechanical components, such as the lens barrel, further clips peripheral light before or after the entrance pupil.

Pixel vignetting is due to a mismatch between the Chief Ray Angle (CRA) of the lens system and the micro-lenses on top of the image sensor pixels. Micro-lenses over the sensor pixels at nadir are more efficient at focusing incident light to the buried photodiode than those closer to the edges of the sensor.

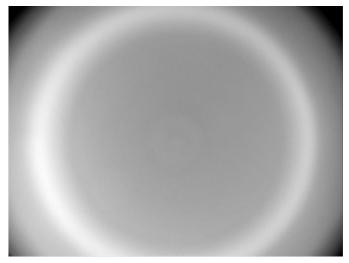

Figure 9: Flat-field image demonstrating strong lens-shading

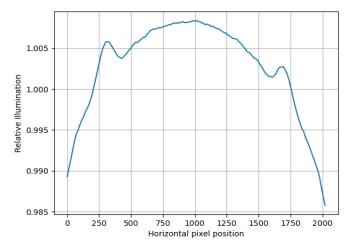

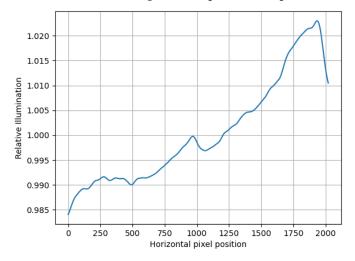

The simple, low-cost solution to correct lens shading is to record a flat-field image (Figure 9) with the lens assembly attached, and record horizontal and vertical intensity profiles across the center of the image. The intensity profiles can be stored in BRAMs, and dedicated horizontal-, and vertical multipliers can correct for intensity drop, preferably on a single channel before CFA interpolation. For a color image, the two sets of multipliers would require a total of 6 DSP48 primitives. For a more optimal solution, the horizontal and vertical correction factors can be pre-combined, then the combined correction coefficient can be applied to all 3 color channels (4 DSP48 primitives).

However, the 2D intensity drop function is rarely separable. A higher-quality, more precise approach is to store a down-sampled ( $32 \times 32$ ) version of the intensity map using a single BRAM primitive. Either bilinear-, or biquadratic interpolation can be used to compute correction factors for streaming pixels. As pixels are accessed in a scanline-continuous order (left to right, top to bottom), the quadratic differential-integrator structure introduced in section 8.4.1 can be used, to create a highly accurate low-cost interpolator.

For cameras with variable lens-, and shutter assemblies the 2D intensity drop-off function is dependent on zoom and aperture settings, which need to be recorded during manufacturing. The optical de-center for each image in the resulting image stack is the same, which enables storing only a few representative samples along the axes (aperture and zoom) to interpolate. Since aperture and zoom is constant for a frame, and is varying relatively slowly due to mechanical actuators, in practical systems the aperture – zoom image stack is down-sampled (e.g., 32x32), and stored in external memory next to the system processor. Camera FW interpolates between sub-sampled (32x32) images using the current aperture and zoom settings and updates the correction coefficients in the ISP lens-shading correction module between frames.

### 2.11 Image de-warping

Wide-angle, fish-eye lenses bend rays more near the edges of the lens than the rays near the center of the lens. Due to radial distortion straight lines in real world appear to be curved on the image. Image de-warping, or camera lens distortion correction compensates for deviation from rectilinear projection.

Figure 10: positive radial distortion (a: calibration pattern, b:barrel distortion, c: model)

The first step of distortion correction is characterizing the camera in a series of calibration steps. In a controlled laboratory-, or manufacturing environment the camera is exposed to checkerboard patterns (Figure 10.a) in different orientations. From the recorded images coordinates of checkerboard square corners are extracted. Using the method introduced in [12] extrinsic and intrinsic camera parameters are established. Using linear correction operations translation, clocking, skewing errors can be compensated, fitting the checkerboard pattern with residual non-linear distortions into to output coordinate system (Figure 10.b).

At this point FPGA-, and ASSP/GPU-based ISP algorithms bifurcate. ASSP/GPUs typically prefer a parametric definition of radial/tangential distortion parameters, which are established using the Brown–Conrady even-order polynomial model, or Fitzgibbon's method [13]. For an FPGA implementation, storing a re-sampled distortion map (Figure 10.c) provides a simple way to avoid divisions and polynomial evaluation.

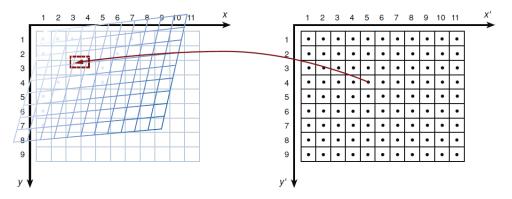

In order to generate a corrected, rectilinear output frame, the exact (sub-pixel) location of each output pixel (x,y) needs to be located in the input frame (x',y'), an operation referred to as backward mapping (Figure 11). Considering that output pixels are generated in a scanline continuous order, the x', and y' coordinates of the distortion grid can be continuously interpolated using the quadratic differential-integrator structure introduced in section 8.4.1, as in the case of lens-shading correction, assuming resampled grid coordinates are stored in respective BRAMs.

Figure 11: Backward mapping of output pixel positions into the input sampling grid

The backward-mapped coordinates typically do not align with the input sampling grid, therefore output pixels have to be interpolated. Considering that no significant downscaling is performed during distortion correction, bilinear interpolation (Figure 12) delivers adequate results with no perceivable aliasing effects.

Figure 12: Bilinear interpolation using 4 nearest neighbors

To perform bilinear interpolation, the backward mapped pixel coordinates (x', y') are quantized to [x'], [y'], where [] denotes the integer part of the coordinates, and the four pixels  $\underline{p} = \{p([x'], [y']), p([x'] + 1, [y']), p([x'], [y'] + 1), p([x'] + 1, [y'] + 1)\}$  are retrieved from memory.

Note that for each output pixel four input pixels have to be retrieved, which demands considerable bandwidth from the frame buffer, typically in external memory (DDR). Additionally, DDR, shared with other processes, is accessed in arbitrated bursts. Reading a set of horizontally adjacent pixels in a read burst is orders of magnitude faster than randomly accessing single pixels in the frame buffer. Therefore, the local neighborhood around [x'], [y'], needs to be cached using BRAMs. Efficient four-way cache design, using dual ported BRAMs, predictively populating the cache before pixels in *p* are accessed, is the key to high performance de-warping.

The remainders,  $u = x' - \lfloor x' \rfloor$ ,  $v = y' - \lfloor y' \rfloor$  are used as coefficients for bilinear interpolation. Coefficient vector  $\underline{c} = \{(1 - u)(1 - v), u(1 - v), (1 - u)v, uv\}$  are used by the bilinear interpolator module, which performs

$$o(x, y) = \underline{c}^T \underline{p} = \sum_{i=1}^4 c_i p_i.$$

(3)

For color image processing with deep colors (10-, or more bits per channel) each color channel may require a bilinear interpolator, allocating 12 DSP48 primitives. For 8 bit color channels, the number of DSP48s can be reduced if the R,G,B components are combined into a single 24 bit logic vector with guard bits between the components {R[7:0], 8'b0, G[7:0]}, and using a single 24x18 multiplier in the DSP48Ex primitive to perform two eight-bit multiplications simultaneously, reducing the number of DSP48 primitives used to 8. Another option, for high-performance FPGA devices is to run the interpolation kernel at 3x the pixel clock rate, processing color channels sequentially.

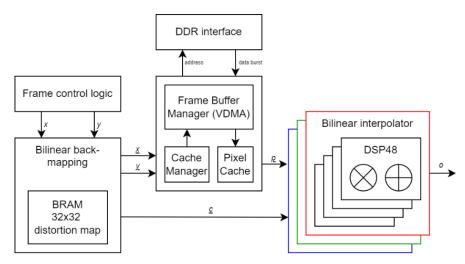

Figure 13 presents the top-level block diagram of lens distortion correction module example for color video streams using dual-ported BRAMs and DSP48 primitives.

Figure 13: Block diagram of a lens-distortion correction module for Xilinx FPGAs

#### 2.12 Video Scaling

Image sensor output formats may differ from typical streaming video formats, such as 720p, 1080p, or 2160p. Modern image sensors also support binning and windowing / Region of Interest (ROI) operations. In binning mode, the sensor aggregates photons captured by adjacent pixels and outputs a lower resolution image with higher SNR. In ROI mode only a rectangular region of the pixel array is read out, enabling faster frame rates. ROI mode is particularly attractive for wide-angle security camera applications implementing digital Pan-Tilt-Zoom (PTZ) features. In order to support a continuously changing input resolution due to ROI zooming, a configurable video-scaling unit is necessary to convert the input to the selected standard output format.

Video scaling is the process by which an input color image  $W_{in}$  pixels wide with  $H_{in}$  scanlines is converted to an output color image of dimensions  $W_{out}$ ,  $H_{out}$ . Similar to de-warping described above, output pixels are backward mapped. To avoid aliasing, instead of a simple bilinear kernel, a 2D filter kernel of size  $W_{taps} \times H_{taps}$ ,  $W_{taps} = 2w + 1$ ,  $H_{taps} = 2h + 1$  ( $h, w \in \mathbb{Z}$ ) is often used:

$$o(x,y) = \sum_{i=-h}^{h} \sum_{j=-w}^{w} c_{i+h,j+w} p(x+j,y+i),$$

(4)

where *x* and *y* are discrete locations on the output sampling grid, and  $c_{i,j}$  are the 2D filter coefficients. The difference between the bilinear, bicubic, and Lanczos interpolation filters are differences in kernel size and coefficients only. For up-scaling applications, a bilinear, or bicubic kernel is usually adequate. However, for down-scaling properly designed low-pass kernels are necessary to avoid aliasing (Moire) artifacts. The size of the filter kernel is proportional to the downscaling ratio, e.g., to downscale  $W_{out} = 0.25W_{in}$  the horizontal size of the kernel needs to span across at least 4 pixels both directions, for  $w \ge W_{in}/W_{out}$ .

For most practical up-sampling/down-sampling kernels a separable low-pass filter is designed simplifying equation (4) to

$$o(x,y) = \sum_{i=-h}^{h} \mu_{i+h} \sum_{j=-w}^{w} \nu_{j+w} p(x+j,y+i),$$

(5)

where  $\mu_i$  are coefficients for the vertical-, and  $\nu_i$  are coefficients for the horizontal filters.

Polyphase implementation of one-dimensional FIR filters greatly reduces the number of taps necessary for high-quality resampling. Conceptually, the space between 2 consecutive input pixels is partitioned into a number of phases. Since the resampling ratio is a rational fraction, the location of any arbitrary output pixel between two input pixels in the sampling grid maps onto a discrete grid, exemplified on Figure 14.

Figure 14: One dimensional resampling from 6 input to 5 output pixels

The 5 output pixels shown from left to right can be interpolated with a two-tap polyphase FIR filter using phases 0..4. In phase 0, the output pixel is co-located with an input pixel, therefore the coefficients for phase 0,  $v[0] = \{1.0, 0.0\}$ . Coefficients for phase 1 are  $v[1] = \{0.2, 0.8\}$ .

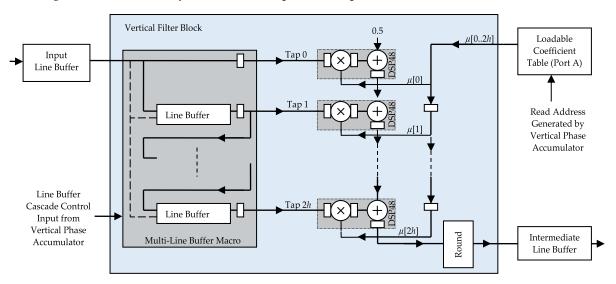

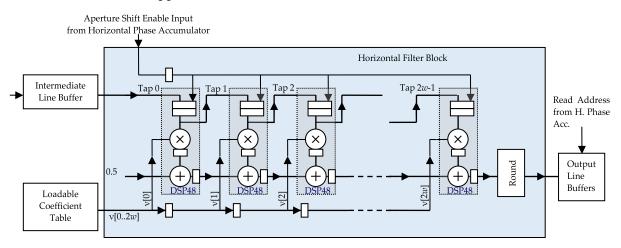

To create a configurable 2D scaler implementing a separable low-pass filter, the vertical (Figure 15) and horizontal (Figure 16) resampling stages need to be cascaded. The vertical filtering stage needs to have access to 2h+1 lines, for which 2h image lines need to be buffered. The horizontal stage consumes the output of the vertical stage via an intermediate buffer, providing parallel access to all pixels in the buffer.

The line buffer macro, implemented using BRAMs, is typically driving the footprint of the video scaler module. Even though the module uses several DSP48 primitives, for high resolution sensors, buffering each video line may consume multiple BRAM primitives.

Figure 15: Example of a vertical scaling FIR filter stage, implemented using DSP48 primitives

For up-scaling (zoom-in) operation, it is beneficial to perform vertical scaling first, then horizontal scaling, while for down-scaling the reverse order is optimal to minimize the line-buffer BRAM allocations.

To complete the scaler design, control logic initialized with the scaling ratio tracks x,y position in the frame, and generates horizontal-, and vertical phase accumulator and shift enable signals. Control logic and filter coefficient initialization typically happens in FW, with coefficients pertinent to actual scaling ratios either precomputed and stored in a filter-bank or computed on the fly.

The polyphase concept, polyphase re-sampling low-pass filter design, and coefficient generation is described in detail in [4] pp. 799-806.

Figure 16: Example of a horizontal scaling FIR filter stage, implemented using DSP48 primitives

#### 2.13 Chroma resampling

For transmission and processing often time camera output is converted to the YUV or YCbCr color-spaces, where *Y* is Luminance information, and U(Cb) and V(Cr) are derived color difference signals. Acuity of human vision for chrominance is less than half of that for luminance, which allows down sampling the chrominance components without perceivable loss of fidelity. Besides reducing transmission and storage loads, storing two pixels with 8 bit color components in a single 32 bit word (Y<sub>0</sub>U<sub>0</sub>Y<sub>1</sub>V<sub>0</sub>) greatly simplifies addressing and aligning pixels with DDR bursts and 32/64 bit memory operations. For video transmission this format is referred to as 422, implying that for 4 adjacent pixels in a 2x2 square over two scanlines 2 chroma components are transmitted in each scanline. On Figure 17, white squares represent luminance (Y) samples, blue circles represent the blue chroma components, and red circles represent the red chroma components.

Figure 17: YUV 444, 422, and 420 transmission and storage formats

For the 444 and 422 formats, chrominance samples are co-sited with luminance samples. However, even for 422, chrominance needs to be horizontally low-pass filtered before down-sampling to avoid chrominance aliasing. The 420 format down-samples by two in the vertical direction as well, transmitting / storing one red, and one blue chrominance components for 2x2 adjacent luminance pixels. For MPEG-2, MPEG-4, and H.264 the 420 standard specifies chrominance sampled between the scanlines [14]. In order to re-sample chrominance, and avoid vertical color aliasing, the chrominance components need to be low-pass filtered with a two-, or four tap vertical anti-aliasing filter. Usually, the chroma samples are generated for every output pixel row, but they are valid only for the even pixel rows. Besides streaming video synchronization signals, a typical chroma down-sampling module provides an additional signal marking valid chroma samples.

Higher level algorithms in machine vision platforms may expect RGB, or Luma and Chroma components stored in different planes / arrays, such as for the NV12 format (Figure 18). In machine vision platforms the output of the ISP is often fed to an image compositor layer, which sorts the streaming components into planes. On an FPGA this may be performed by the last stage of the chroma re-sampler, optionally collecting luminance and chrominance samples in different line-buffers. Line buffer outputs in turn can feed separate video DMA write engines, set up such that write transfers are deposited into adjacent memory arrays.

Figure 18: NV12 component planes

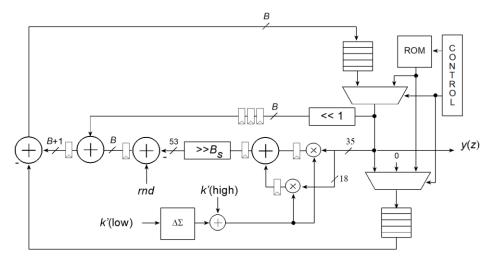

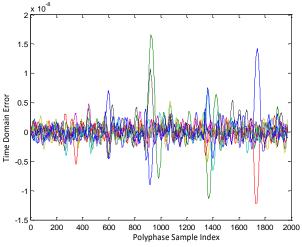

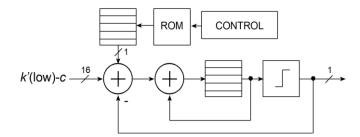

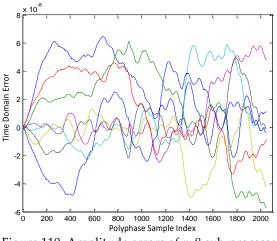

#### 2.14 ISP Sensor Control